#### Error Correction Method Based On The Short-Duration Offline Test

#### Jan Bělohoubek, Petr Fišer, Jan Schmidt

${\tt jan.belohoubek, petr.fiser, jan.schmidt} @fit.cvut.cz$

Czech Technical University in Prague Prague, Czech Republic

DSD 2016, Limassol - Cyprus

#### Faculty of Information Technology

#### What?

- Combine time and area redundancy to achieve error-correction

- Reduce the number of required test vectors from thousands to tens

- Why?

- To reduce the total system costs

- To reduce the test time and the test-hardware complexity

- Employ an extremely short offline test short-duration offline test

- Describe the circuit properties required for the short-duration test

- Propose special hardware structures enabling the short-duration test

Faculty of Information Technology

# What?

- Combine time and area redundancy to achieve error-correction

- Reduce the number of required test vectors from thousands to tens

Why?

- To reduce the total system costs

- To reduce the test time and the test-hardware complexity

- Employ an extremely short offline test short-duration offline test

- Describe the circuit properties required for the short-duration test

- Propose special hardware structures enabling the short-duration test

Faculty of Information Technology

# What?

- Combine time and area redundancy to achieve error-correction

- Reduce the number of required test vectors from thousands to tens

# Why?

- To reduce the total system costs

- To reduce the test time and the test-hardware complexity

- Employ an extremely short offline test short-duration offline test

- Describe the circuit properties required for the short-duration test

- Propose special hardware structures enabling the short-duration test

Faculty of Information Technology

# What?

- Combine time and area redundancy to achieve error-correction

- Reduce the number of required test vectors from thousands to tens

# Why?

- To reduce the total system costs

- To reduce the test time and the test-hardware complexity

- Employ an extremely short offline test short-duration offline test

- Describe the circuit properties required for the short-duration test

- Propose special hardware structures enabling the short-duration test

Faculty of Information Technology

### What?

- Combine time and area redundancy to achieve error-correction

- Reduce the number of required test vectors from thousands to tens

# Why?

- To reduce the total system costs

- To reduce the test time and the test-hardware complexity

- Employ an extremely short offline test short-duration offline test

- Describe the circuit properties required for the short-duration test

- Propose special hardware structures enabling the short-duration test

Faculty of Information Technology

# What?

- Combine time and area redundancy to achieve error-correction

- Reduce the number of required test vectors from thousands to tens

Why?

To reduce the total system costs

To reduce the test time and the test-hardware complexity

- Employ an extremely short offline test short-duration offline test

- Describe the circuit properties required for the short-duration test

- Propose special hardware structures enabling the short-duration test

Faculty of Information Technology

# What?

- Combine time and area redundancy to achieve error-correction

- Reduce the number of required test vectors from thousands to tens

To reduce the total system costs

o educe the test time and newsest-hardware complexity

# How?

Employ an extremely short offline test – short-duration offline test

Why?

- Describe the circuit properties required for the short-duration test

- Propose special hardware structures enabling the short-duration test

Faculty of Information Technology

# What?

- Combine time and area redundancy to achieve error-correction

- Reduce the number of required test vectors from thousands to tens

To reduce the total system costs

ounduce the test time and est-hardware complexity

# How?

Employ an extremely short offline test – short-duration offline test

Why?

- Describe the circuit properties required for the short-duration test

- Propose special hardware structures enabling the short-duration test

Faculty of Information Technology

# What?

- Combine time and area redundancy to achieve error-correction

- Reduce the number of required test vectors from thousands to tens

- To reduce the total system costs

- To reduce the test time and the test-hardware complexity

# How?

Employ an extremely short offline test – short-duration offline test

Why?

- Describe the circuit properties required for the short-duration test

- Propose special hardware structures enabling the short-duration test

Faculty of Information Technology

# What?

- Combine time and area redundancy to achieve error-correction

- Reduce the number of required test vectors from thousands to tens

Why?

- To reduce the total system costs

- To reduce the test time and the test-hardware complexity

- Employ an extremely short offline test short-duration offline test

- Describe the circuit properties required for the short-duration test

- Propose special hardware structures enabling the short-duration test

Faculty of Information Technology

# What?

- Combine time and area redundancy to achieve error-correction

- Reduce the number of required test vectors from thousands to tens

Why?

- To reduce the total system costs

- To reduce the test time and the test-hardware complexity

- Employ an extremely short offline test short-duration offline test

- Describe the circuit properties required for the short-duration test

- Propose special hardware structures enabling the short-duration test

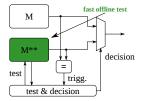

Fundamental Ideas Error-Correction

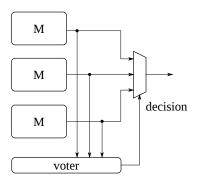

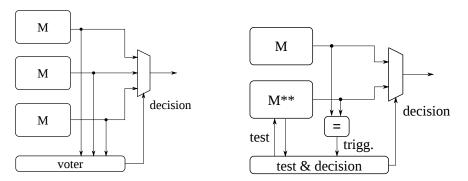

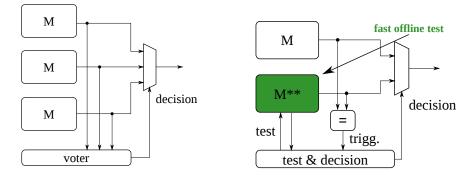

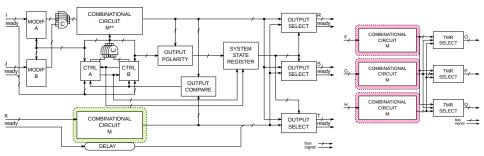

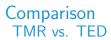

#### The most popular solution – TMR

Fundamental Ideas Error-Correction

The most popular solution – TMR  The proposed solution – *Time-Extended Duplex* (TED)

Fundamental Ideas Error-Correction

The most popular solution – TMR  The proposed solution – *Time-Extended Duplex* (TED)

#### Fundamental Ideas Short-Duration Offline Test

What is required:

Error Correction Method Based On TheShort-Duration Offline Test

### Fundamental Ideas Short-Duration Offline Test

What is required:

the test length in orders of tens of computational (clock) cycles only

### Fundamental Ideas Short-Duration Offline Test

What is required:

- the test length in orders of tens of computational (clock) cycles only

- 100% fault coverage

### Fundamental Ideas Short-Duration Offline Test

What is required:

- the test length in orders of tens of computational (clock) cycles only

- 100% fault coverage

$\rightarrow$  short-duration offline test

### Fundamental Ideas Short-Duration Offline Test

What is required:

- the test length in orders of tens of computational (clock) cycles only

- 100% fault coverage

- $\rightarrow$  short-duration offline test

- → special hardware structures

Observation Stuck-At-Fault Model

Only two test vectors are required to achieve 100% fault-coverage: *all-zero* and *all-one* vector

#### Theorem

There is a two-vector-testable class of circuits with respect to the stuck-at-fault model.

Observation Stuck-At-Fault Model

Only two test vectors are required to achieve 100% fault-coverage: *all-zero* and *all-one* vector

#### Theorem

There is a two-vector-testable class of circuits with respect to the stuck-at-fault model.

Required circuit properties:

■ A monotonic circuit contains no inverters → fault symptom cannot change during propagation

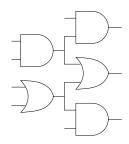

### Observation Stuck-At-Fault Model

Required circuit properties:

- A monotonic circuit contains no inverters → fault symptom cannot change during propagation

- The circuit conforms the *indication principle* → every gate output is connected to at least one AND and one OR gate

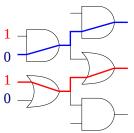

Observation Stuck-At-Fault Model

stuck-at-1 / fault symptom: 1

stuck-at-0 / fault symptom: 0

Required circuit properties:

- A monotonic circuit contains no inverters → fault symptom cannot change during propagation

- The circuit conforms the *indication principle* → every gate output is connected to at least one AND and one OR gate

Observation Stuck-At-Fault Model

Only two test vectors are required to achieve 100% fault-coverage: *all-zero* and *all-one* vector

#### Theorem

There is a two-vector-testable class of circuits with respect to the stuck-at-fault model.

Required circuit properties:

- A monotonic circuit contains no inverters → fault symptom cannot change during propagation

- The circuit conforms the *indication principle*  $\rightarrow$  every gate output is connected to at least one AND and one OR gate

- $\rightarrow$  Every stuck-at-fault is observable

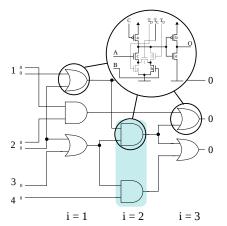

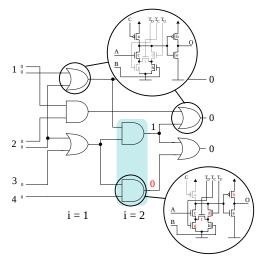

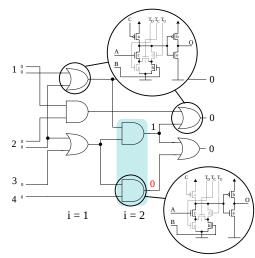

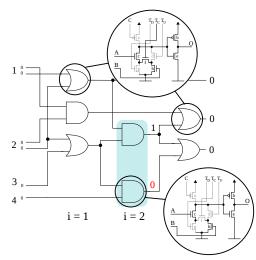

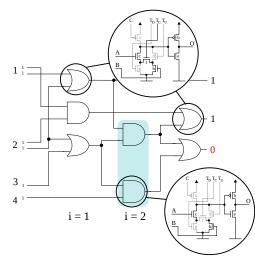

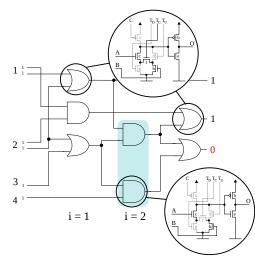

Efficient Monotonic Circuit Circuit Transformation

How to build the circuit complying with the "required properties"

- Make the circuit monotonic employ dual-rail logic

- Reconfigurable gates OR/AND gate

- + less gates

- + fault symptoms at the fault-affected wires

- reconfigurable gate  ${\sf OR}/{\sf AND}$  is complex

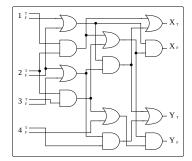

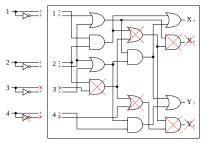

### Efficient Monotonic Circuit Dual-Rail Implementation

Efficient Monotonic Circuit Dual-Rail Implementation

Faculty of Information Technology

**Efficient Monotonic Circuit Dual-Rail Implementation**

If the dual-rail logic serves as the inverter replacement only, the number of gates can be reduced

of Information Technology

Information Technology

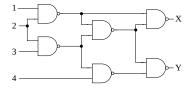

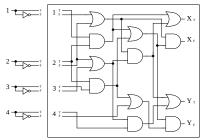

Efficient Monotonic Circuit Dual-Rail Reduction

- If the dual-rail logic serves as the inverter replacement only, the number of gates can be reduced

- The number of gates can be the same as in the single-rail implementation (in the best case)

nformation Technology

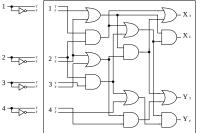

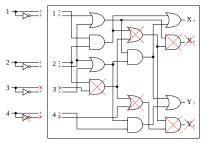

Efficient Monotonic Circuit Dual-Rail Reduction

- If the dual-rail logic serves as the inverter replacement only, the number of gates can be reduced

- The number of gates can be the same as in the single-rail implementation (in the best case)

- Sometimes is the output polarity optional this affects the *reduction success* → heuristics were developed

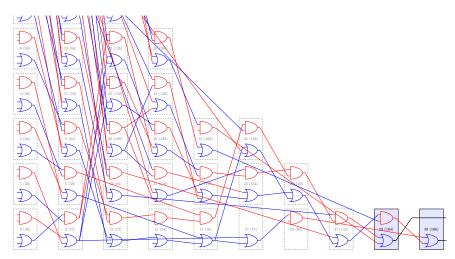

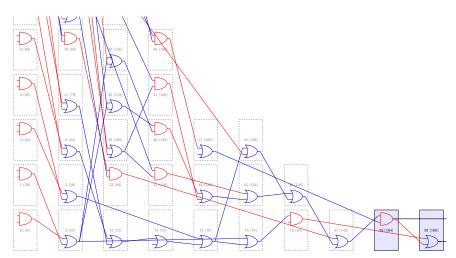

# Dual-Rail Reduction Positive outputs only (Cordic benchmark)

Faculty of Information Technology

Dual-Rail Reduction Greedy heuristic (Cordic benchmark)

Faculty of Information Technology

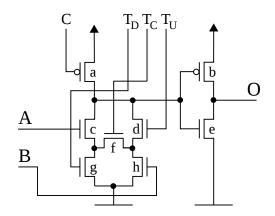

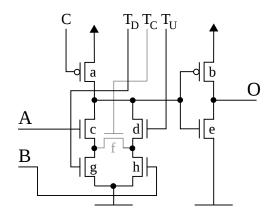

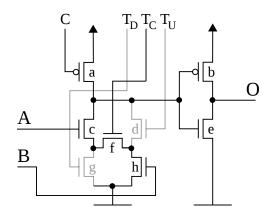

Reconfigurable Gate Design

Faculty of Information Technology

Domino-logic AND/OR gate with increased controlability

Reconfigurable Gate Design

Faculty of Information Technology

Domino-logic OR gate  $T_D = 1$ ,  $T_C = 0$ ,  $T_U = 1$

Reconfigurable Gate Design

Faculty of Information Technology

Domino-logic AND gate  $T_D = 0$ ,  $T_C = 1$ ,  $T_U = 0$

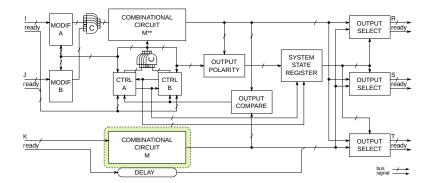

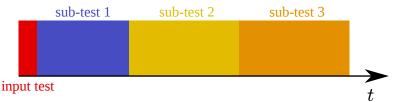

#### The Offline Test Overview

- Combinational logic test

- $\blacksquare$  Test of the reconfiguration is required o longer test

- Inspired by two-vector-testability; uses the state-holding property and the increased controlability of dynamic gates

- Test of all stuck-open/stuck-on faults

- The test length remains in orders of tens computational cycles only

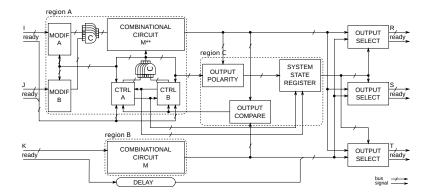

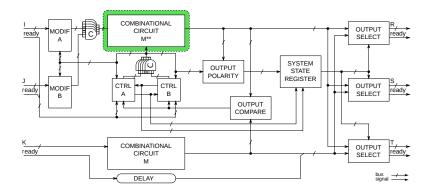

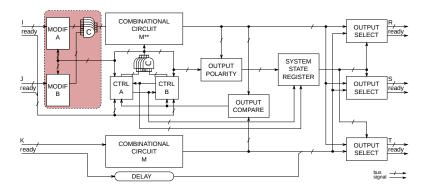

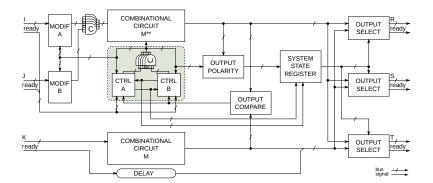

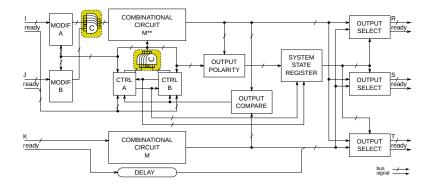

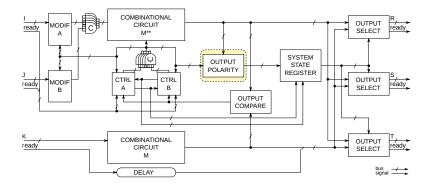

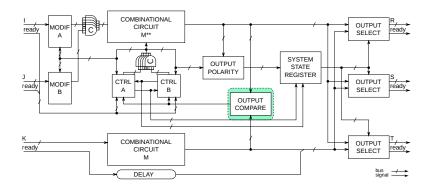

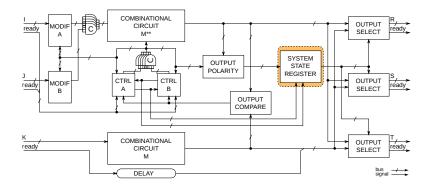

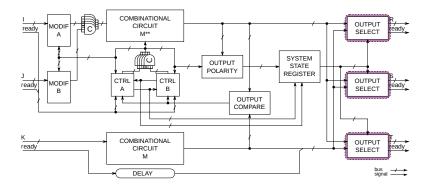

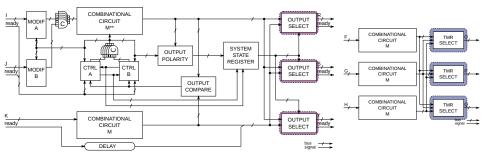

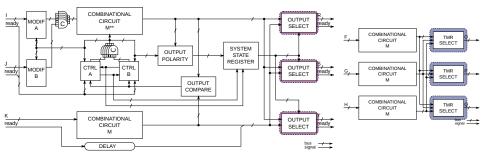

Structure of the TED Original Combinational Part

#### Structure of the TED Offline-Testable Combinational Part

Structure of the TED Single-Rail to Dual-Rail and Test Input Gen.

#### Structure of the TED Test Control Part

Structure of the TED Duplex Checkers

#### Structure of the TED Test Response Evaluation

Structure of the TED Test Trigger

#### Structure of the TED Last Test Results

#### Structure of the TED Corect Output Selection

| step | С                                      | Τυ                              | T <sub>C</sub> | T <sub>D</sub>     | 0            |  |  |

|------|----------------------------------------|---------------------------------|----------------|--------------------|--------------|--|--|

| 1    |                                        | set circuit primary inputs to 0 |                |                    |              |  |  |

| 2    |                                        |                                 | star           | t at level $i=1$   |              |  |  |

| 3    |                                        |                                 | a              | at all levels:     |              |  |  |

|      | 0                                      | 0                               | 0              | 0                  | $\downarrow$ |  |  |

| 4    |                                        | at level <i>i</i> :             |                |                    |              |  |  |

|      | 1                                      | 1                               | 1              | 1                  | $\uparrow$   |  |  |

| 5    | at level <i>i</i> :                    |                                 |                |                    | 1            |  |  |

|      | 1                                      | 0                               | 0              | 0                  | 1            |  |  |

| 6    | at levels other than i:                |                                 |                |                    |              |  |  |

|      | 1                                      | 0                               | 1              | 0                  | 0            |  |  |

| 7    | set circuit primary inputs to 1        |                                 |                |                    |              |  |  |

| 8    | Check if the circuit output is all-one |                                 |                |                    |              |  |  |

| 9    |                                        | if (+                           | ·+i ≤          | depth) then goto 3 | 1            |  |  |

| step | С                                      | 0                   | T <sub>C</sub> | T <sub>D</sub>     | 0 |  |  |

|------|----------------------------------------|---------------------|----------------|--------------------|---|--|--|

| 1    | set circuit primary inputs to 0        |                     |                |                    |   |  |  |

| 2    | start at level $i = 1$                 |                     |                |                    |   |  |  |

| 3    |                                        |                     | a              | at all levels:     |   |  |  |

|      | 0                                      | 0 0 0 0             |                |                    |   |  |  |

| 4    |                                        | at level <i>i</i> : |                |                    |   |  |  |

|      | 1                                      | 1                   | 1              | 1                  | 1 |  |  |

| 5    | at level <i>i</i> :                    |                     |                |                    | 1 |  |  |

|      | 1                                      | 0                   | 0              | 0                  | 1 |  |  |

| 6    | at levels other than <i>i</i> :        |                     |                |                    |   |  |  |

|      | 1                                      | 0                   | 1              | 0                  | 0 |  |  |

| 7    | set circuit primary inputs to 1        |                     |                |                    |   |  |  |

| 8    | Check if the circuit output is all-one |                     |                |                    |   |  |  |

| 9    |                                        | if (+               | ·+i ≤          | depth) then goto 3 | 1 |  |  |

| step | С                                      | 0     | T <sub>C</sub> | T <sub>D</sub>     | 0          |  |

|------|----------------------------------------|-------|----------------|--------------------|------------|--|

| 1    | set circuit primary inputs to 0        |       |                |                    |            |  |

| 2    | start at level $i = 1$                 |       |                |                    |            |  |

| 3    |                                        |       | á              | at all levels:     |            |  |

|      | 0 0 0 0                                |       |                |                    |            |  |

| 4    | at level <i>i</i> :                    |       |                |                    |            |  |

|      | 1                                      | 1     | 1              | 1                  | $\uparrow$ |  |

| 5    | at level <i>i</i> :                    |       |                |                    | 1          |  |

|      | 1                                      | 0     | 0              | 0                  | 1          |  |

| 6    | at levels other than <i>i</i> :        |       |                |                    |            |  |

|      | 1                                      | 0     | 1              | 0                  | 0          |  |

| 7    | set circuit primary inputs to 1        |       |                |                    |            |  |

| 8    | Check if the circuit output is all-one |       |                |                    |            |  |

| 9    |                                        | if (+ | ·+i ≤          | depth) then goto 3 | 1          |  |

| step | С                                      | Τυ                  | T <sub>C</sub> | T <sub>D</sub>     | 0          |  |  |

|------|----------------------------------------|---------------------|----------------|--------------------|------------|--|--|

| 1    | set circuit primary inputs to 0        |                     |                |                    |            |  |  |

| 2    |                                        |                     | star           | t at level $i=1$   |            |  |  |

| 3    |                                        |                     | á              | at all levels:     |            |  |  |

|      | 0                                      | 0 0 0 0             |                |                    |            |  |  |

| 4    |                                        | at level <i>i</i> : |                |                    |            |  |  |

|      | 1                                      | 1                   | 1              | 1                  | $\uparrow$ |  |  |

| 5    | at level <i>i</i> :                    |                     |                |                    | 1          |  |  |

|      | 1                                      | 0                   | 0              | 0                  | 1          |  |  |

| 6    | at levels other than <i>i</i> :        |                     |                |                    |            |  |  |

|      | 1                                      | 0                   | 1              | 0                  | 0          |  |  |

| 7    | set circuit primary inputs to 1        |                     |                |                    |            |  |  |

| 8    | Check if the circuit output is all-one |                     |                |                    |            |  |  |

| 9    |                                        | if (+               | -+i ≤          | depth) then goto 3 | 1          |  |  |

| step | С                                      | Τυ                              | T <sub>C</sub> | T <sub>D</sub>      | 0          |  |  |

|------|----------------------------------------|---------------------------------|----------------|---------------------|------------|--|--|

| 1    |                                        | set circuit primary inputs to 0 |                |                     |            |  |  |

| 2    |                                        |                                 | star           | t at level $i = 1$  |            |  |  |

| 3    |                                        |                                 | a              | at all levels:      |            |  |  |

|      | 0                                      | 0 0 0 0                         |                |                     |            |  |  |

| 4    |                                        |                                 |                | at level <i>i</i> : | 0          |  |  |

|      | 1                                      | 1                               | 1              | 1                   | $\uparrow$ |  |  |

| 5    | at level <i>i</i> :                    |                                 |                |                     | 1          |  |  |

|      | 1                                      | 0                               | 0              | 0                   | 1          |  |  |

| 6    | at levels other than <i>i</i> :        |                                 |                |                     |            |  |  |

|      | 1                                      | 0                               | 1              | 0                   | 0          |  |  |

| 7    | set circuit primary inputs to 1        |                                 |                |                     |            |  |  |

| 8    | Check if the circuit output is all-one |                                 |                |                     |            |  |  |

| 9    |                                        | if (+                           | ·+i ≤          | depth) then goto 3  | 1          |  |  |

| step | С                                      | Τυ                     | T <sub>C</sub> | T <sub>D</sub>      | 0          |  |  |

|------|----------------------------------------|------------------------|----------------|---------------------|------------|--|--|

| 1    | set circuit primary inputs to 0        |                        |                |                     |            |  |  |

| 2    |                                        | start at level $i = 1$ |                |                     |            |  |  |

| 3    |                                        |                        | a              | at all levels:      |            |  |  |

|      | 0                                      | 0 0 0 0                |                |                     |            |  |  |

| 4    |                                        |                        |                | at level <i>i</i> : | 0          |  |  |

|      | 1                                      | 1                      | 1              | 1                   | $\uparrow$ |  |  |

| 5    | at level <i>i</i> :                    |                        |                |                     | 1          |  |  |

|      | 1                                      | 0                      | 0              | 0                   | 1          |  |  |

| 6    | at levels other than <i>i</i> :        |                        |                |                     |            |  |  |

|      | 1                                      | 0                      | 1              | 0                   | 0          |  |  |

| 7    | set circuit primary inputs to 1        |                        |                |                     |            |  |  |

| 8    | Check if the circuit output is all-one |                        |                |                     |            |  |  |

| 9    |                                        | if (+                  | -+i ≤          | depth) then goto 3  | 1          |  |  |

# The Offline Test Length

Faculty of Information Technology

$$(2t_e) + (dt_e) + (t_e + dt_e) + (t_e + dt_e)$$

$t_{tot} \leq (3d+4) \cdot t_e$

- Classical test  $>> 1000 \cdot t_e$

- Proposed test  $< 100 \cdot t_e$

- $t_e$  computational (clock) cycle time; d circuit depth

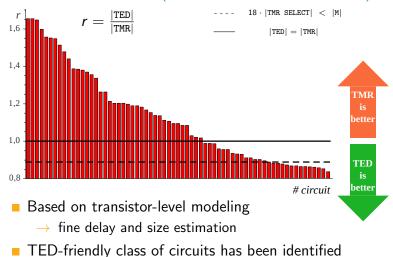

$18 \cdot |\text{TMR SELECT}| < |M|$

mation Technology

Comparison Results (IWLS'2005 benchmark circuits)

- The principle of the short-duration offline test was presented

- Novel gate structure allowing the offline test was introduced

- The novel error-correcting design method combining time and area redundancy was developed (TED)

- The efficient monotonic circuit implementation was presented

- Usage of the TED was suitable (compared to the TMR system) for circuits having relatively large combinational parts and small number of outputs

# What happens when ...?